5.3 KiB

使用 ModelSim 进行时序仿真

准备工作

首先需要 EDA 综合工具生成用于功能或时序仿真的网表文件(VHDL为.vho,Verilog为.vo),以及使用 EDA 仿真工具进行时序仿真时所需要的包含时序延时信息的标准延时格式输出文件(.sdo)。

这里我们以 EDA 工具为 ALTERA 的 Quartus II 9.0 为例,使用 Verilog DHL,讲解如何使用 Quartus II 9.0 生成 ModelSim 6.2b 时序仿真所需的.vo及.sdo 文件。这里我们先使用 EDA 工具对工程进行综合,综合通过后进行如下操作。

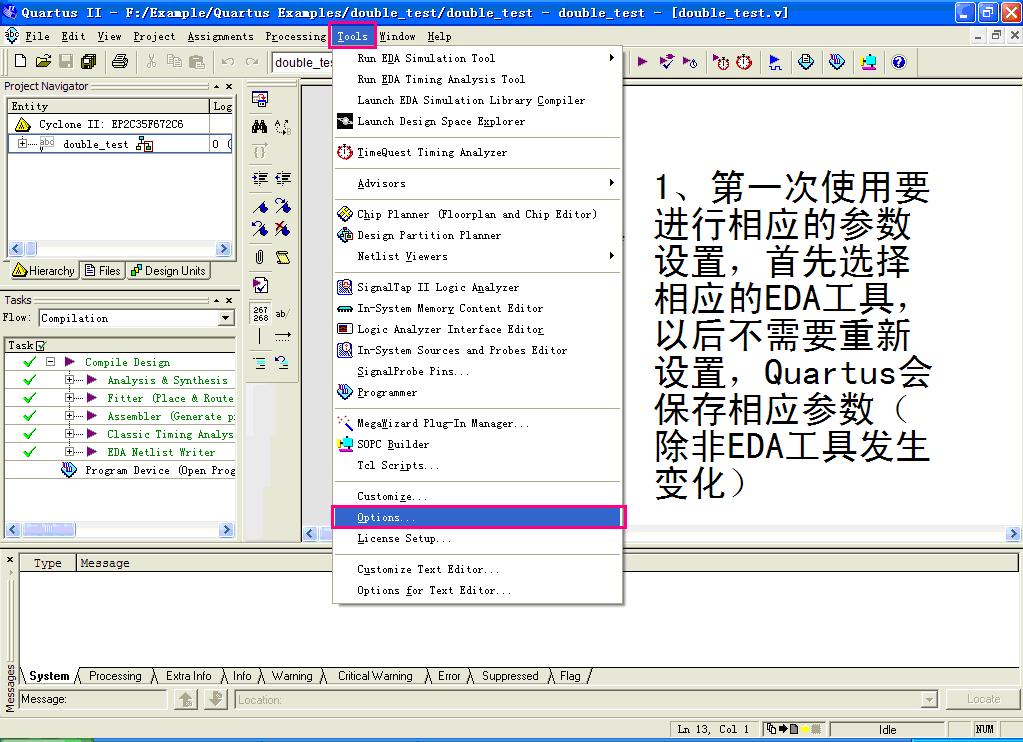

1、设置仿真工具的路径。

设置用户存放 ModelSim 的路径,选择菜单栏的 Tools-->Options,如下图所示:

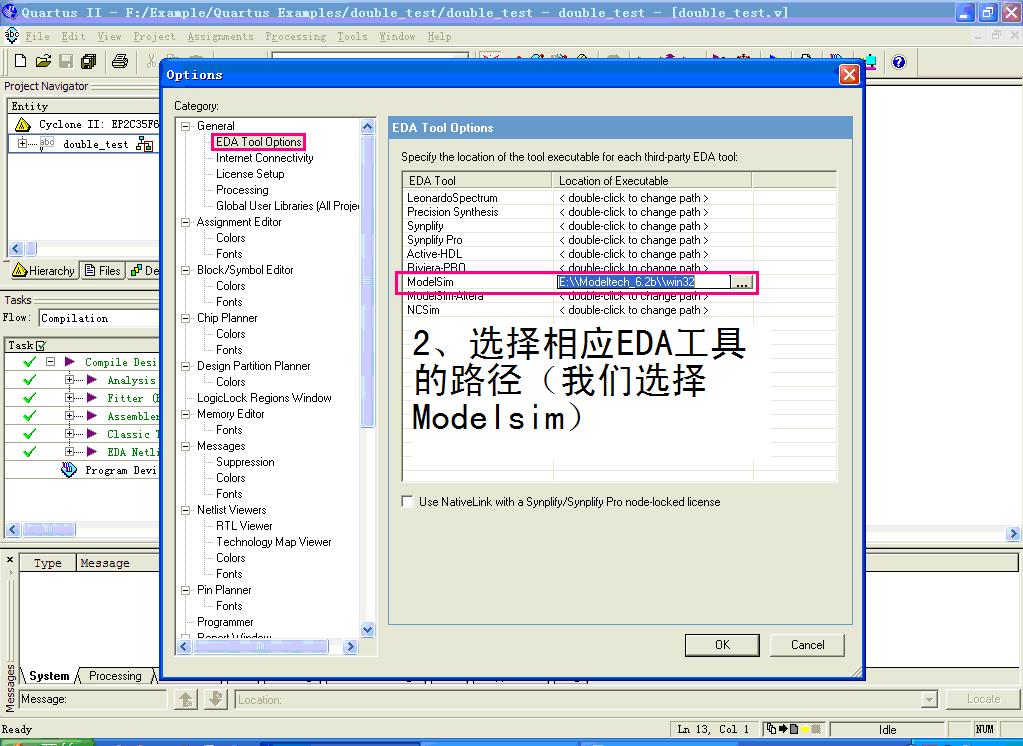

在 Options 窗口下,选择左栏 Category 下的 General-->EDA Tools Options,则右栏出现相应的仿真工具。我们选择 ModelSim,并设置路径(该路径为用户存放 ModelSim 的路径),完成后单击 OK。如下图所示:

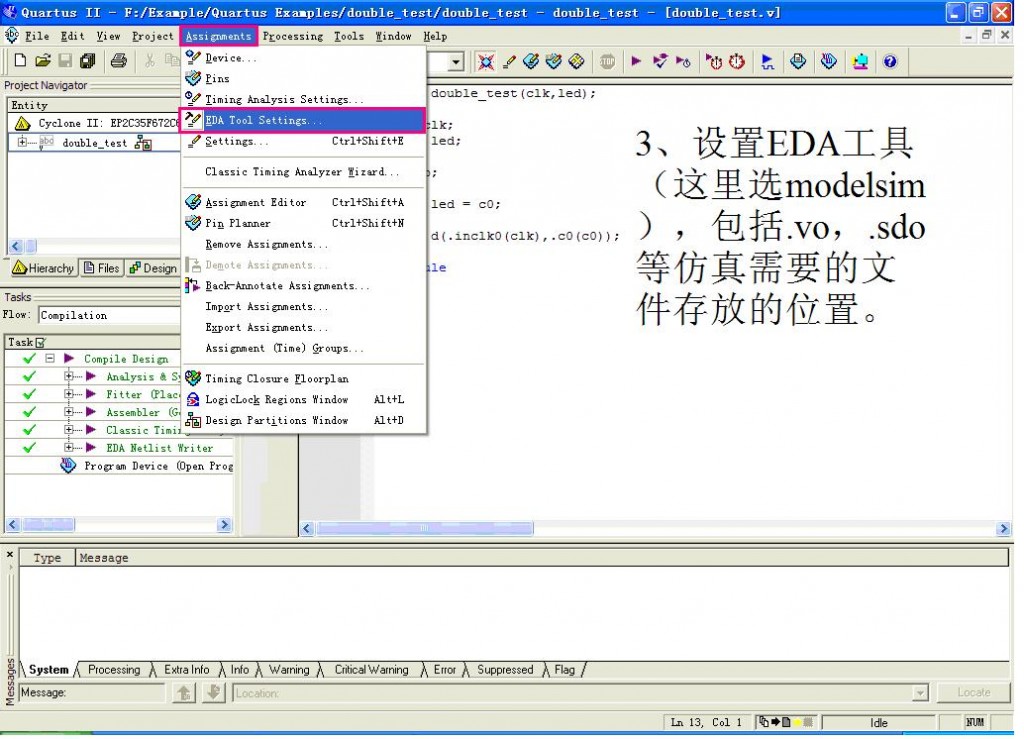

2、设置生成文件存放的位置。

选择菜单栏的 Assignments-->EDA Tools Settings,如下图所示:

此时我们进入相应的状态栏,选择左栏 Category 下的 EDA Tools Options-->Simulation,在 Tool name 选择 ModelSim,其他 Format for output netlist 选择 Verilog,其它使用默认参数。完成后单击 OK。如下如所示:

至此,再次进行综合,在工程路径下的 simulation/modelsim 将生成后仿真(也称时序仿真)所需的网表文件(.vo)及延时文件(.sdo)。

ModelSim 进行时序仿真

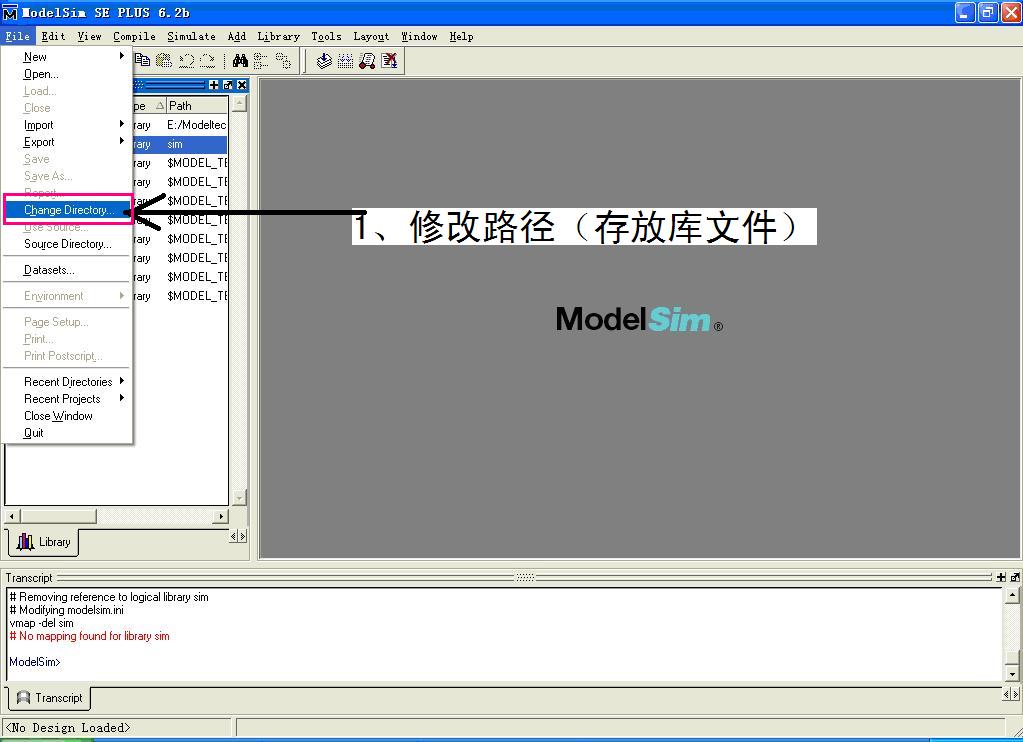

1、打开 ModelSim,修改存放编译后库文件的位置。

选择菜单栏 File-->Change Directory,如下图所示。第一次需要编译,以后只需要调用该库文件就行,不需要重新编译(前提是使用该库支持,后面将介绍我们编译的库支持资源)。

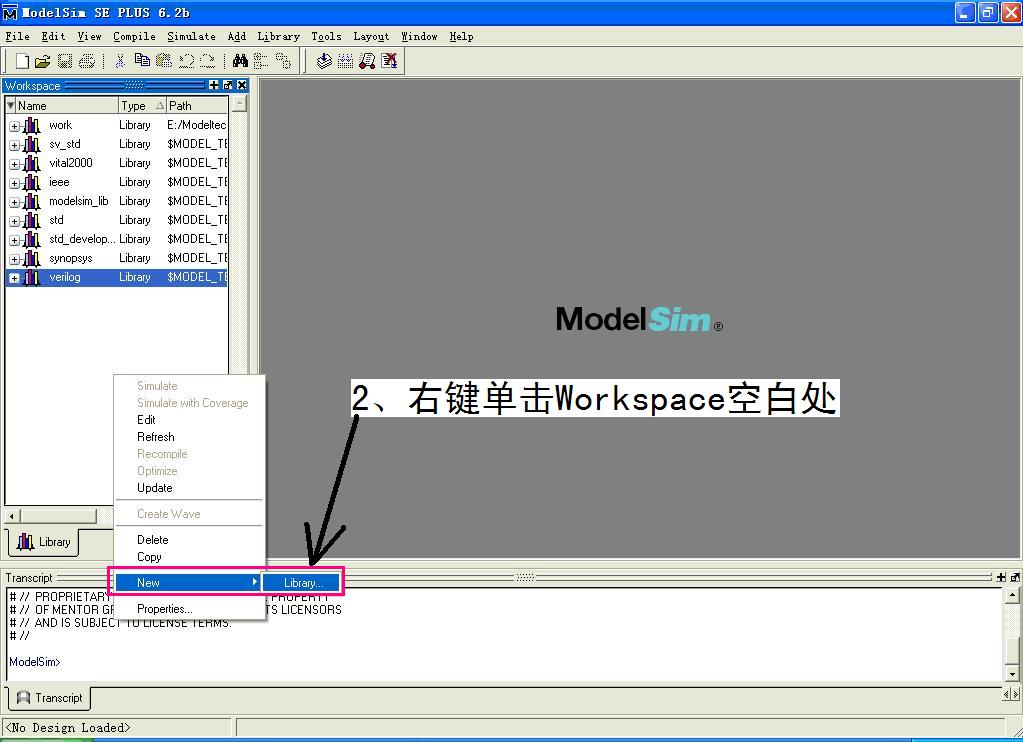

2、建立库文件。

在 Workspace 窗口中 Library 的空白处单击鼠标的右键,选择 New-->Library,如下图所示:

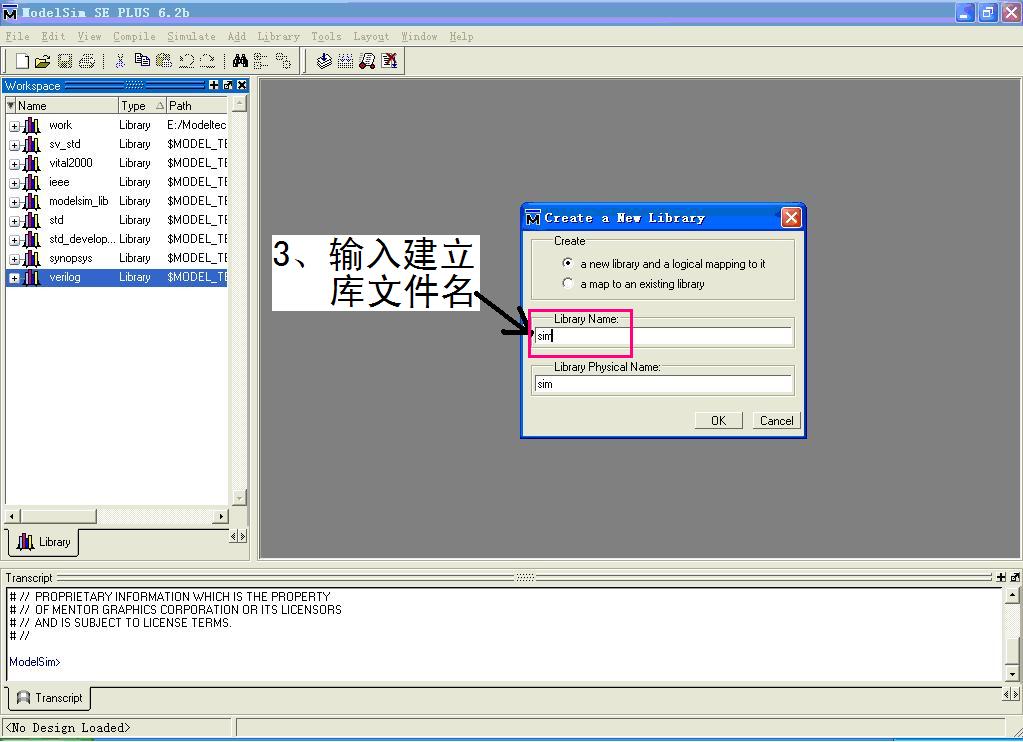

3、输入相应的库文件名字。

在 Library Name 输入库文件的名字,用户可自由输入,这里我们输入 sim,并选择 a new library and a logical mapping to it,单击 OK,如下图所示:

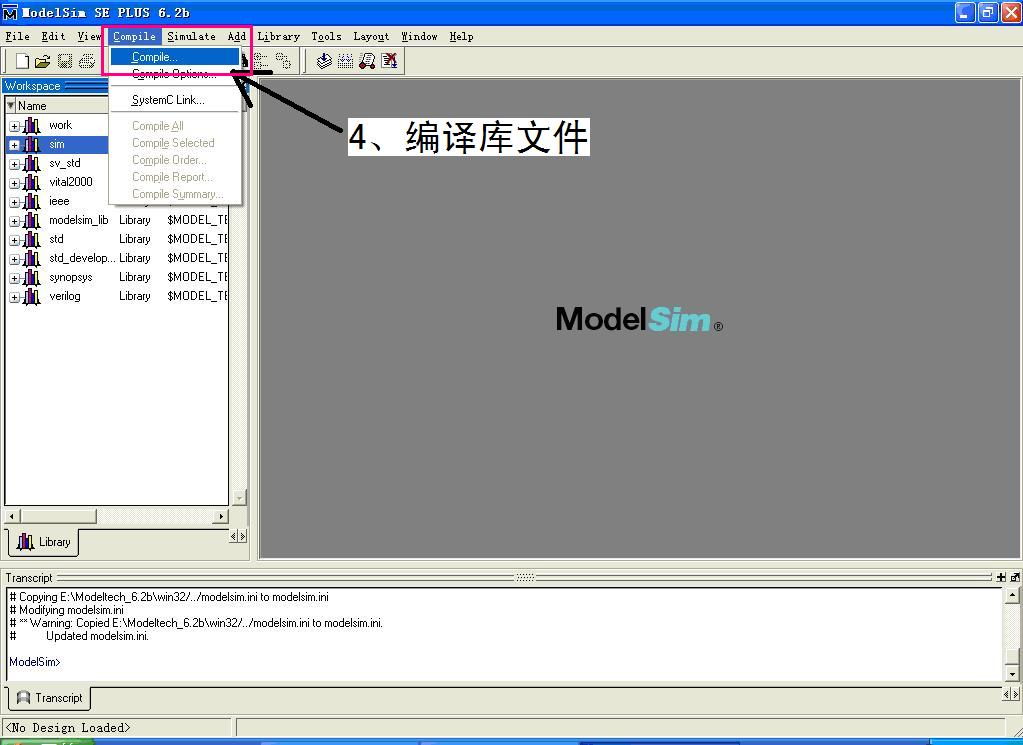

4、开始编译 EDA 工具的资源。

在 Workspace 选择用户之前建立的库文件(我们选择 sim),并选择菜单栏的 Compile-->Compile,如下图所示:

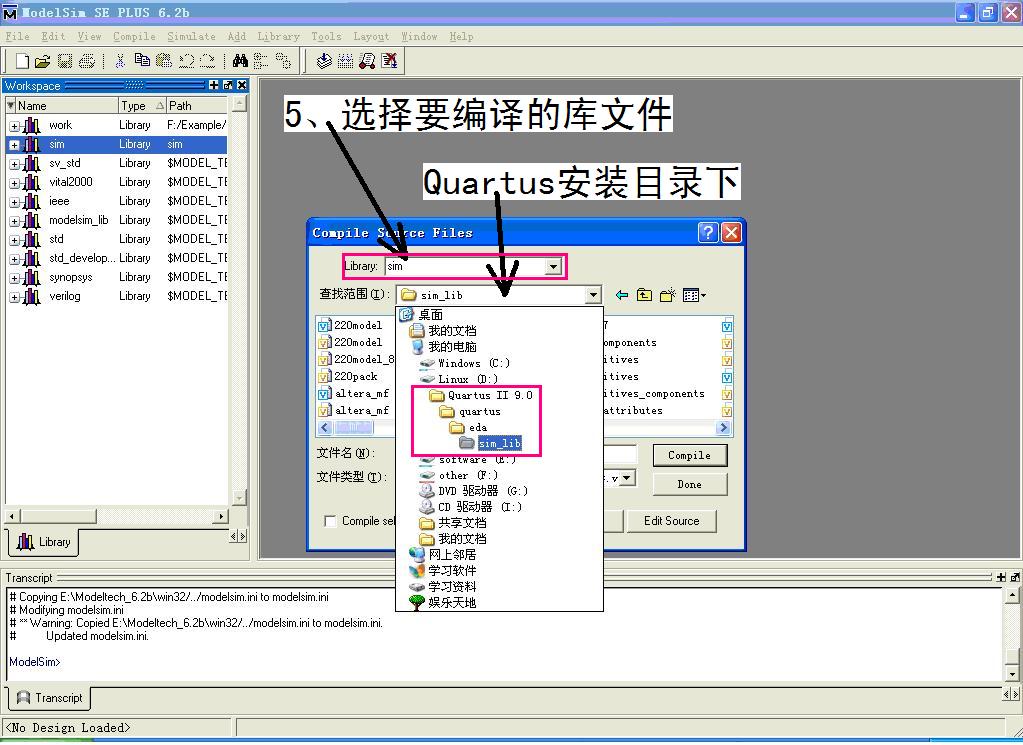

5、选择需编译资源的目录。

由于我们使用的是 ALTERA 的资源,EDA 工具为 Quartus。选择 Quartus 安装目录下的 quartus-->eda-->sim_lib。如下图所示:

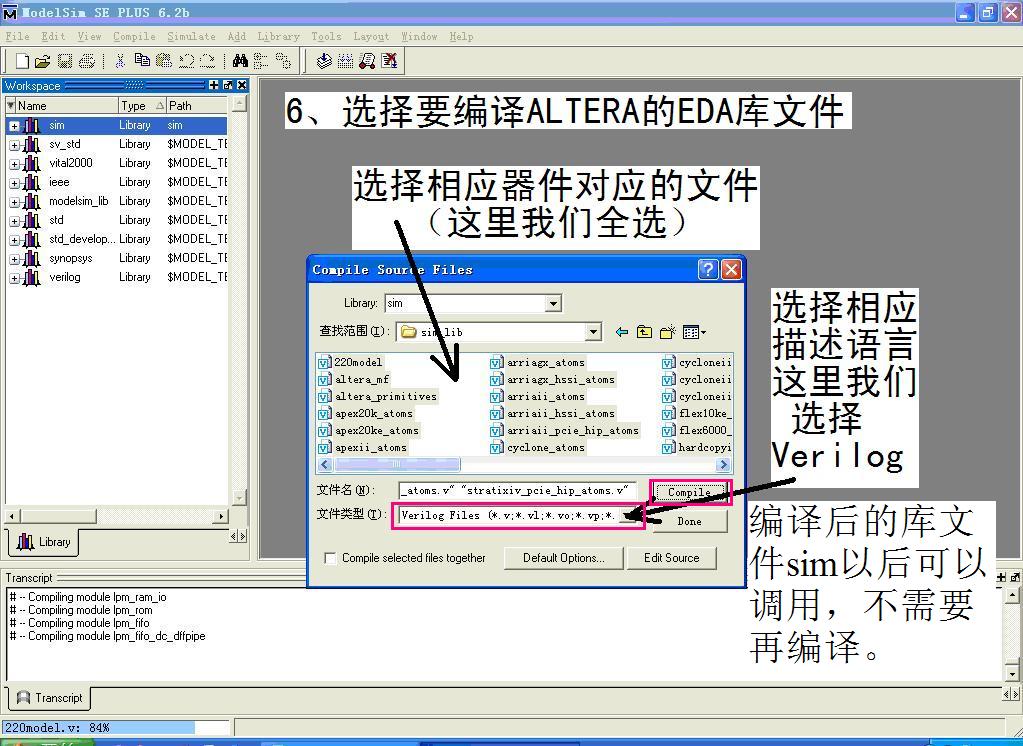

6、选择相应的器件及使用语言。

文件名:我们可以选择部分需要的器件,也可以选择全部器件的资源,这里我们选择全部器件的资源,日后用户无论使用什么器件都只需要调用该文件就行,不需要重新编译,若用户使用的器件资源,在本次编译中没有编译,则需重新选择器件资源进行编译。

文件类型:选择用户编译的语言,可以使 Verilog HDL 或者 VHDL,同器件资源选择一样,日后若是同一种语言,不需要重新编译库文件,调用该库文件就行。这里我们选择 Verilog Files。

确定文件名跟文件类型后,点击 Compile 进行编译。如下图所示:

7、建立工程并添加文件。

编译完成后,建立工程并添加网表(以 Verilog 为例.vo)及激励文件(以 Verilog为例.v),并选择菜单栏的 Simulate-->Start Simulation。这里我们以倍频时钟为例,如下图所示:

8、选择激励。

在 Start Simulation 窗口中选择激励,准备仿真。在 Design-->work 目录下,如下图所示:

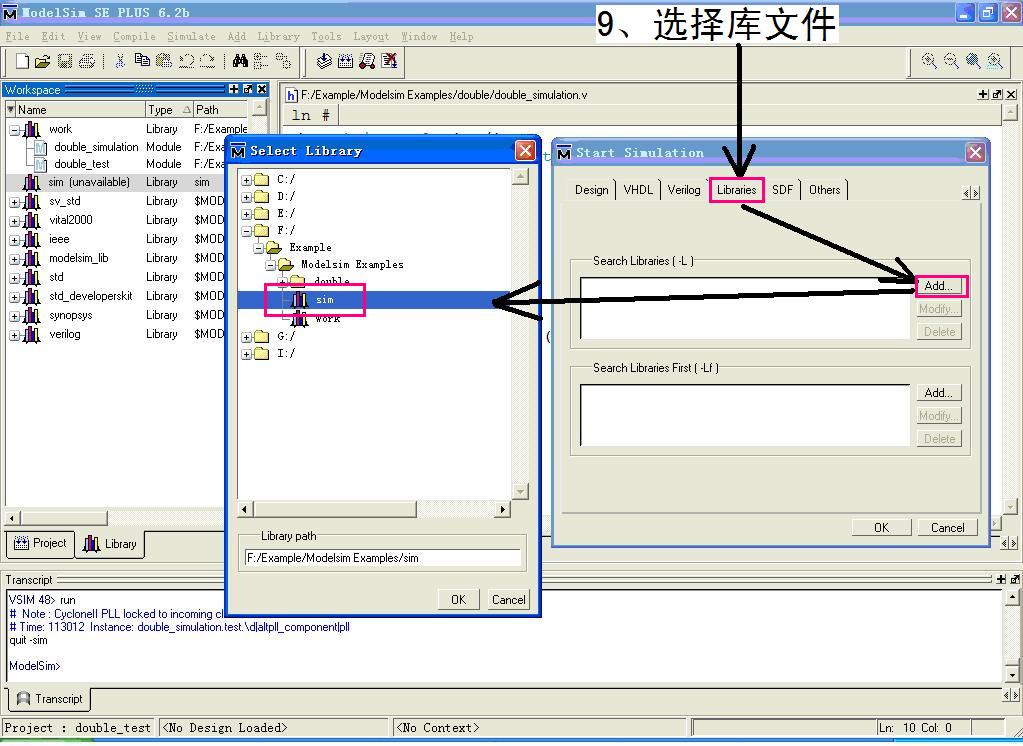

9、添加库文件。

在 Start Simulation 窗口中选择 Libraries,单击 Add,添加我们之前编译的库文件(我们选择 sim),单击 OK,如下图所示:

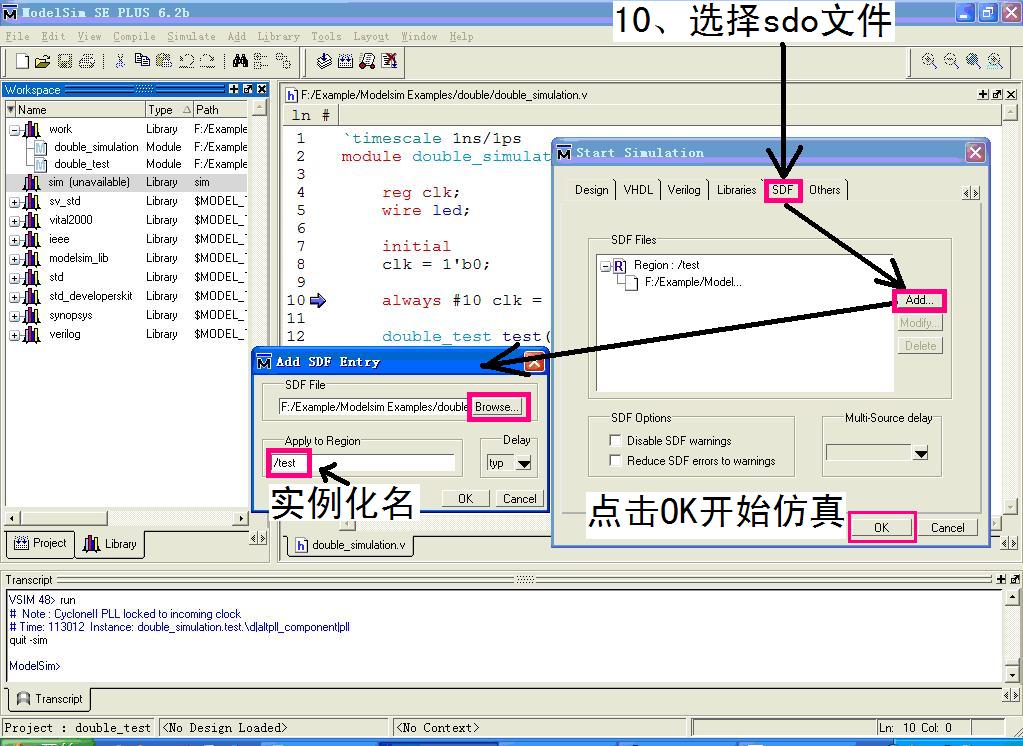

10、添加延时文件。

在 Start Simulation 窗口中选择 SDF,选择包含延时信息的文件(.sdo),在 Browse 选择路径,在 Apply to Region 输入实例化的名字(.v 及.sdo 都是由 EDA 工具生成)。完成后单击 OK 进行仿真。如下图所示:

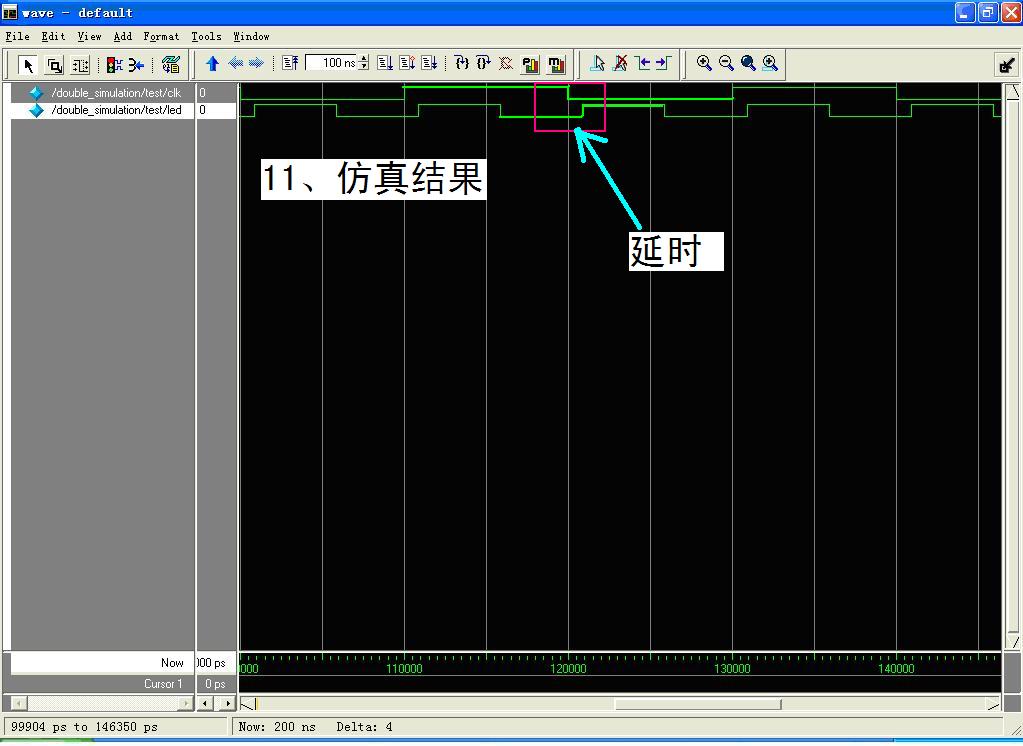

11、仿真结果。

从 wave 中可以看到波形图,仿真结果包含延时信息。